# THERMAL CYCLING RELIABILITY ASSESSMENT OF A CERAMIC COLUMN GRID ARRAY<sup>1</sup> PACKAGE FOR SPACE APPLICATIONS<sup>2</sup>

Rajeshuni Ramesham, Ph.D.

Component Engineering and Assurance Office, Office of Safety and Mission Success Jet Propulsion Laboratory, California Institute of Technology 4800 Oak Grove Dr., Mail Stop 11-111 Pasadena, CA 91109, USA e-mail: *Rajeshuni.Ramesham@jpl.nasa.gov*

# ABSTRACT

Ceramic column grid array (CCGA) packages have been used increasingly in logic and microprocessor functions, telecommunications, flight avionics boards, payload electronics boards, engineering navigational and science cameras, electronic assemblies, and other applications, because of their inherent advantages such as high electrical interconnect density, very good thermal and electrical performance, and compatibility with standard surface-mount technology (SMT) packaging assembly processes. Because these advanced electronic packages tend to have less solderjoint strain-relief than do leaded flat-pack electronic packages, the reliability of CCGA packages in challenging thermal environments is a very important consideration for their short- and long-term use in JPL-NASA space missions.

In this study, we assembled daisy chains of polyimide printed wiring boards from CCGA-interconnect packages, inspected the boards nondestructively, and then subjected them to thermal cycling to assess their reliability in thermal environments from  $+125^{\circ}$ C to  $-40^{\circ}$ C $\pm 25^{\circ}$ C.

The test hardware consists of a CCGA 1752 package (CN version). The package was divided into four daisy-chained sections that were electrically monitored for their continuity during thermal cycling. The CCGA 1752 package is roughly 45 mm  $\times$  45 mm with a 42-mm  $\times$  42-mm array of 80%/20% Pb/Sn columns on a 1.00-mm pitch. The resistance of the daisy-chained CCGA interconnects was continuously monitored during thermal cycling in a gaseous nitrogen environment. Electrical continuity resistance measurements as a function of thermal cycling are reported here; tests to date have shown significant change to an open circuit in daisychain resistance as a function of thermal cycling. The change in interconnect resistance becomes increasingly noticeable with increasing number of thermal cycles. This paper describes the experimental thermal-cycling test results of CCGA 1752 package reliability testing under an extremely wide temperature range. The first failure was observed at 1479<sup>th</sup> thermal cycle. We report the thermal-cycle reliability test data for ~2500 thermal cycles.

**Key words**: Ceramic column grid array, CCGA 1752 (CN version) qualification, CCGA reliability, solder-joint failures, thermal cycling

#### INTRODUCTION

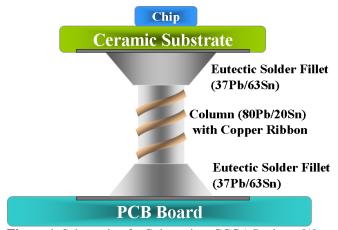

Ceramic column grid array (CCGA) technology is an advanced electronic interconnection packaging surfacemount technology (SMT) process. This advanced CCGA interconnect technology will significantly improve the performance of avionics/electronics systems. The failure mechanisms of CCGA interconnects are dependent on the materials of the columns and board, the solder-joint at the column/ceramic interface, column/board material interface, solder reflow temperature, and the solder materials employed. The most predominant failure mechanism is solder-joint fatigue during thermal cycling. Any coefficient of thermal expansion (CTE) mismatch between board material and columns or between columns and ceramic substrate causes shear displacement at each of the solder-joint interconnects, which may lead to fatigue failure during low thermal cycles, as well as during power cycling. Figure 1 shows the schematic of the 80Pb/20Sn column with copper spiral configuration in the CCGA package [1].

# STATE-OF-THE-ART CCGA RELIABILITY

CCGA packaging interconnect technology was first introduced by IBM to enhance the reliability of electronic

<sup>&</sup>lt;sup>1</sup> Virtex-5 CCGA 1752 Kyocera Package (CN version).

<sup>&</sup>lt;sup>2</sup> ©2016 California Institute of Technology. Government sponsorship acknowledged.

packaging interconnects over ball grid array (BGA) technology [2]. CCGA assembly and rework is described in depth in an IBM user guide [2] and elsewhere [3, 4].

The CCGA package allows direct electrical connection between a device module and a printed wiring board (PWB). Master [5] has reported the CCGA for flip-chip applications in temperature ranges of 0°C to +100°C and -55°C to +125°C. In this study, it was demonstrated that the column height and temperature cycling conditions were in agreement with the Coffin-Manson relationship. Aeroflex [6] has tested a 472-column CCGA daisy-chained package in a temperature range of -55°C to +105°C for 500 thermal cycles and observed fractures in solder-joints at the board side, although some boards showed higher resistance. Kuang and Zhao [7] have reported thermal-cycling test results of CCGA electronic packages that exceed the reliability requirements of satellite program applications. They reported reliability tests (at -55°C to +105°C) for two column material configurations, 90Pb/10Sn<sup>3</sup>, and 80Pb/20Sn with copper spiral<sup>4</sup>. The results showed that the 80Pb/20Sn column material is more reliable over the 90Pb/10Sn column material. The test was stopped at 2,300 thermal cycles with no failures for the 80Pb/20Sn column material. For the 90Pb/10Sn column material, the first failure was observed at 1246 thermal cycles. Ghaffarian [8] reported that CCGA 717 input/output (I/O) modules showed minimal signs of solderjoint damage at 500 thermal cycles from -55°C to +100°C but showed various levels of damage at 1000 thermal cycles with the same temperature limits. The corner columns, without staking, showed a higher damage level compared to their counterparts with staking. No failures were observed for CCGA 717 I/O assemblies after 200 thermal cycles in a range of -120°C to +85°C and also from -65°C to +150°C. [9-11] Tasooji et al. [12] have reported on the design parameters that influence the reliability and sensitivity of CCGA assemblies. Actel has also published and presented CCGA reliability findings for space applications [13, 14] Lau and Dauksher have reported on the reliability of a 1657 CCGA with leadfree solder [15].

Ghaffarian [16] has recently reviewed the state-of-the-art reliability for space applications of a number of CCGAs. His paper lists the failure mechanisms of CCGAs 1752, 1509, 1272, and 1144 under accelerated thermal cycling conditions. He discusses potential failure sites at solder-joint interfaces such as package, printed circuit board (PCB), and column. Topline has provided a summary of literature on the reliability of CCGA packaging technology [17]. Mattsson [18] has reported the thermal cycling data for CCGA packaging under 500 cycles according to ECSS-Q-70-08A (- $55^{\circ}C$  to  $+100^{\circ}C$ ). No cracks were observed along the circumference of the column at the PCB-column interface, but cracks were observed at interposer side. Test coupons were thermal-cycled from -55°C to +125°C for 500 thermal cycles by Claize et al. [19]. Test coupons manufactured using Chip Carrier Mounting Device (CCMD) columns 0.022 inches in diameter, 0.5 inches high, and with a 52-I/O leadless ceramic chip carrier (LCCC) and glass-epoxy PWB survived 500 thermal cycles. The change in resistance during the 500 thermal cycles met failure criteria in every test coupon studied. Based on test results and simulations, solder balls are about twice as effective at conducting heat as are micro springs, as reported by Allison et al. [20]. This was expected in vacuum conditions, but not in no vacuum conditions. Temperatures are slightly lower in no vacuum than in true vacuum ambient temperature in the test area. Problems that can result from a poorly designed board or from a poorly controlled assembly process include voiding in the solder joints, bent pins from mishandling, misalignment of the CCGA, incomplete solder wetting, lack of solder fillet, and solder shorts between the columns, as reported by Alcorn et al. [21]. CCGA arrays of more than 100 columns can be very large, with many of the solder joints hidden and impossible to inspect via conventional optical imaging or inspection methods. It is normally easy to visually find some defects in the outer row of the array, but workmanship defects in the center of the array cannot be observed without radiographic or x-ray inspection. An effective workmanship evaluation requires capable tools, experienced operators, and knowledge of the limitations of these inspection techniques [21]. Fleisher and Willing [22] have reported Sn/Pb solder joints that are susceptible to creep-fatigue damage when the solder is placed under any thermomechanical stress. Furthermore, when the mechanical loading on the solder joint changes direction, this creep-fatigue damage is increased as the solder is essentially "work-hardened". Both repeated cyclical application and changing direction of the tensional loading on a solder joint result in solder-joint fatigue. A classic cause of such solder-joint fatigue is temperature cycling of soldered hardware when there is a difference between the CTE for the part and that for the support substrate or PWB material. When soldered materials have different CTEs, temperature changes whether caused by changes in the external environment or by power switching/cycling produce substantial cyclic strains within the solder [22].

Solder-joint stress levels observed in CCGAs during thermal cycling are markedly lower than those of BGAs. CTE mismatch causes high-stress points at all four corners of the CCGA assembly. In Fabula's evaluation of a CF1509 package [24], thermal cycling as a part of qualification testing was user-terminated at 1200 cycles, with the CCGA assembly intact. The assembly might have survived even more cycles; however, only 1200 cycles were required to qualify the CCGA for a target of 7 years of operational life in low Earth orbit. Fabula developed an assembly process capable of producing CCGA solder joints that can survive in space in a warm-box enclosure with temperature variation from  $0^{\circ}$ C to +40°C. This estimated reliability was with 90% confidence [24]. Fabula arrived at this finding based on temperature cycling test Condition B (-55°C to +125°C) followed by 25°C electrical test on fully electrically

<sup>&</sup>lt;sup>3</sup> From British Aerospace Engineering (BAE).

functional die. 14 of14 test units passed electrical testing at 1000-, 1500-, 2000-, 3000-, and 4000-thermal-cycle read points [24].

Numerous planetary targets for NASA missions require thermally uncontrolled hardware to operate under extremely cold or hot temperatures with large diurnal temperature changes from day to night: Titan (-180°C, for a proposed Titan in-situ mission), Europa (-160°C, for a proposed Europa surface and subsurface mission), asteroids (-185°C, for Mu Space Engineering Spacecraft C), comets (-140°C, for a proposed comet nucleus sample return), Earth's Moon (-233°C to +123°C, for Moon Mineralogy Mapper), and Mars (-120°C to +85°C for Mars Exploration Rovers; -135°C to +85° for Mars Science Laboratory; and-135°C to +85°C for Mars 2020). Moreover, planetary protection requirements dictate that hardware destined for any of these targets must be baked before flight at +125°C for 72 hours to kill any microorganisms that could contaminate them, especially for sample-return missions. NASA's standard thermal-cycling temperature range is from  $-55^{\circ}$ C to  $+100^{\circ}$ C [25]. The present advanced high-density CCGA 1752 package reliability study uses this temperature range for thermal cycling to cover the thermal requirements of various potential NASA missions [1].

Based on existing published data, to the best of the author's knowledge there is limited published systematic experimental data available to assess the reliability of CCGA packages in low and high temperatures between -55°C and +125°C. This paper describes the important experimental test results obtained in this extreme temperature range for CCGA 1752 (CN version) packages.

#### FABRICATION OF TEST BOARDS

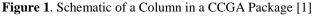

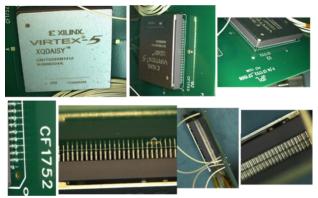

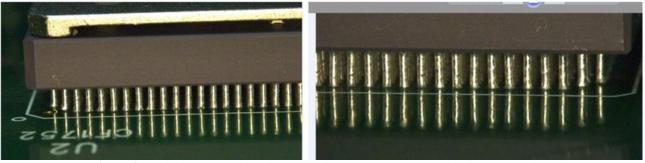

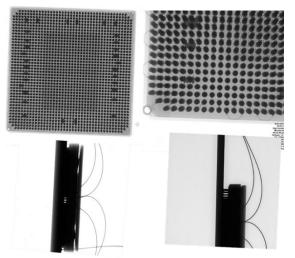

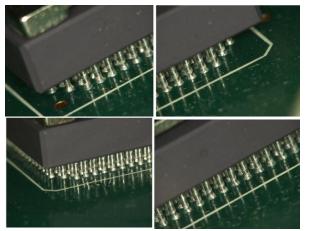

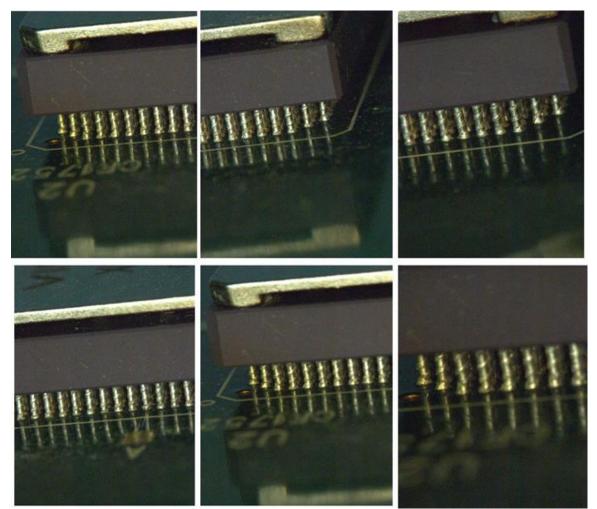

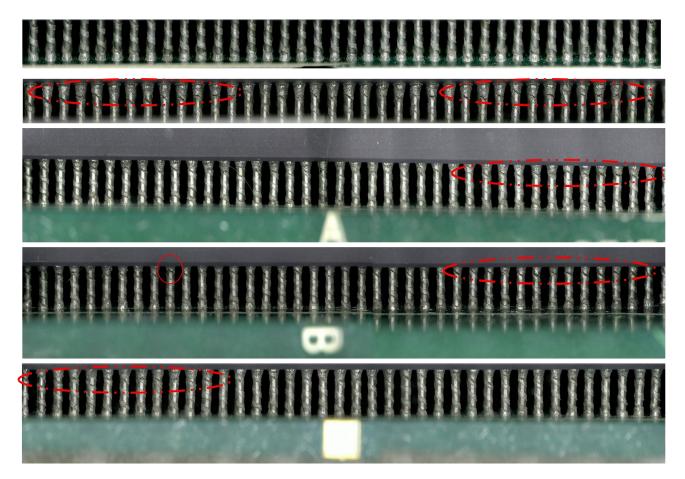

The test boards were fabricated using SMT processes reported by Mehta and Bodie [3, 4]. They developed a process to qualify CCGA package assemblies using PWBs and daisy-chained CCGA 1752 (CN version) packages. Figure 2 shows optical photographs of our as-received CCGA packages prior to reflow and the reflowed packages at various magnifications. A complete CCGA 1752 array package is also shown in Figure 2. Copper spirals can be seen around the column interconnect material. The copper spiral is designed to increase the integrity of the column interconnect during the solder reflow process. Figure 3 shows digital photographs of CCGA packages after they have been reflowed over the PWB. The complete CCGA package is magnified in Figure 3, showing the columns and the copper spirals around the columns. Figure 4 shows nondestructive x-ray images of the CCGA packages after solder reflow. There were no shorts and no overflow of solder materials that could affect the reliability of the CCGA packages, as is clear from the x-ray images.

**Figure 2**. Optical Images of the CCGA Test Board before Thermal Cycling

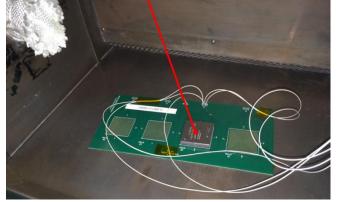

#### **TEMPERATURE PROFILE**

Figure 5 shows the temperature profile employed for thermal cycling of the daisy-chained CCGA-interconnect test boards. The lowest temperature used was  $-40^{\circ}\pm 25C$ , and the highest temperature used was  $+125^{\circ}C$ . The temperature ramp rate was  $5^{\circ}C$  per minute, and dwell time was 30 minutes on hot and cold temperatures during thermal cycling.

#### TESTING FOR OVERSTRESS INTERCONNECT FRACTURE AND INTERMITTENT FAILURES

Figure 6 shows the CCGA 1752 daisy-chained test board in a thermal atmospheric chamber that has been interfaced with the data logger<sup>5</sup> to monitor the solder-joint resistance vs. thermal cycling. There were four daisy chains on this test board, one for each CCGA daisy-chain package. The value of the daisy-chain resistance was about ~2  $\Omega$  at room temperature. Testing was conducted to assess the advanced CCGA-interconnect technology's robustness to solder-joint failure. The key failure mechanism addressed in thermal

Figure 3. Optical Cross-Sectional Images of the CCGA Test Board before Thermal Cycling

<sup>5</sup> Agilent.

Figure 4. X-Ray Image of the CCGA 1752 Daisy-Chain Test Board

cycling was solder-joint fracture at the board-and-column interface or at the column-and-ceramic-package-substrate surface. Temperature cycling in a gaseous nitrogen environment could result in thermal fatigue of the solder joint, and interdiffusion at the substrate, the column, or the column-and-substrate interface. The thermal stress depends on magnitude of the temperature (either on the hightemperature or low-temperature side), rate of temperature change, and range of temperature change (Delta T:  $\Delta$ T), as well as the CTE of the materials combed in the configuration. High rate of temperature change (change in temperature per minute) could lead to thermal shock of the CCGA packages, which could have a catastrophic effect on the reliability of solder joints. Therefore, a low rate of temperature change (5°C per minute) was employed in this study. Figures 2 and 3, which show the CCGA test board before thermal cycling, are comparable to Figure 7, which shows the CCGA 1752 packages after 623 thermal cycles. No solder-joint issues were noted during or after 623 thermal cycles.

**Figure 6.** Optical Digital Image of the CCGA 1752 Daisy-Chain Test Board

Figure 5. Extreme-Temperature Thermal Cycling Profile Used in This Study

Figure 7. Optical Image of the CCGA 1752 Packagesafter 623 Thermal Cycles

Figure 8. Optical Image of the CCGA 1752 Packages after 1460 Thermal Cycles

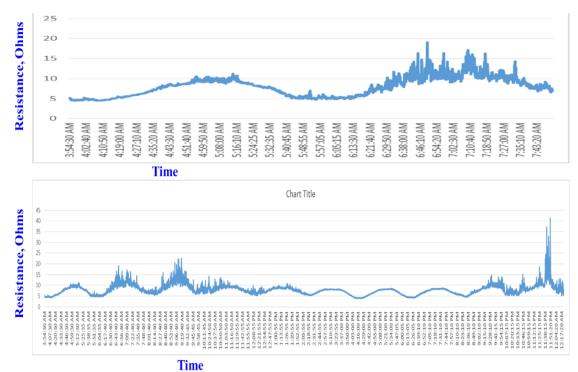

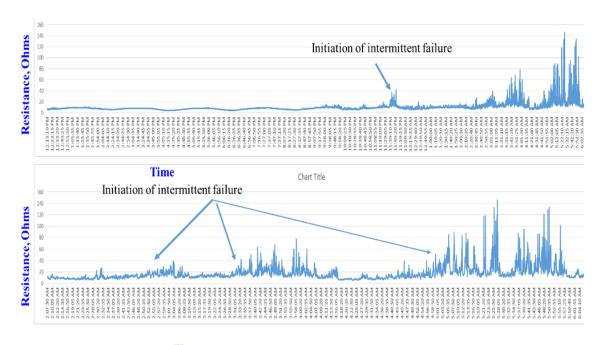

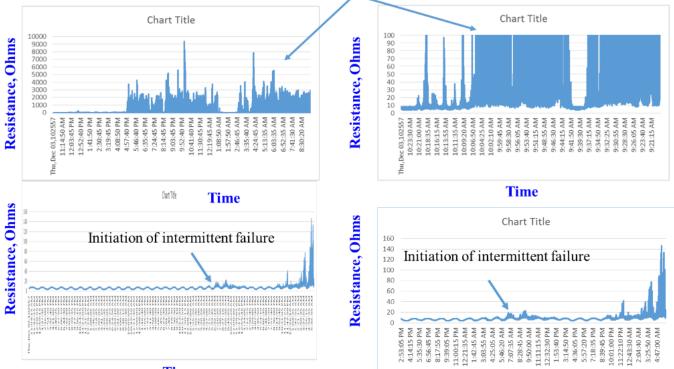

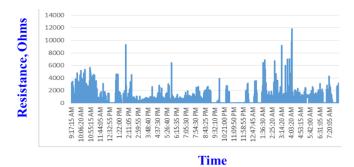

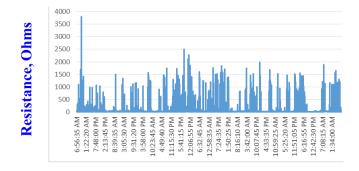

Figure 8 shows the optical image of the columns of CCGA 1752 packages after 1460 thermal cycles. No continuity issues were noted during or up to 1460 thermal cycles. After 1479 thermal cycles, however, we started to observe intermittent failures. Figure 9 shows the resistance of the daisy chains as a function of temperature cycling. Resistance of the solder joint increases as the temperature increases and decreases as the temperature decreases. Figure 9 shows the initiation of intermittent solder joint failures observed at 1479 cycles. Figure 10 shows the resistance of solder joints as a function of thermal cycles. The first solder joint failure was observed at the 1479<sup>th</sup> thermal cycle. The resistance of one of the daisy chains increased

beyond 2 ohms and also beyond 100 ohms, as shown in Figures 10 and 11. More pronounced intermittent failures are shown in Figure 11. The increased resistance of the daisy chain to more than 10,000 ohms certainly provides reason to conclude that the daisy chain has failed. Figures 11 and 12 show the intermittent change in resistance to a higher value when the test article reached hot and cold temperatures for different daisy chains. The cause of daisy-chain failure during the hot and cold portion of the thermal cycle is clear. After 2500 thermal cycles, several daisy chains failed or cracked, as seen in Figures 13 and 14.

Figure 9. Daisy-Chain Resistance vs. Temperature during Thermal Cycling around 1479th Cycle

**Time Figure 10.** Daisy-Chain Resistance vs. Temperature during Thermal Cycling around 1479<sup>th</sup> Cycle

## **Continuous Intermittent failure**

Time

**Figure 11.** Daisy-Chain Resistance vs material. For the 90Pb/10Sn column material, the first failure was observed at 1246 thermal cycles. Ghaffarian [8] reported that CCGA 717 input/output (I/O) modules showed. Time during Thermal Cycling around 1479<sup>th</sup> Cycle.

Figure 12. Resistance vs. Time around 1479th Thermal Cycle

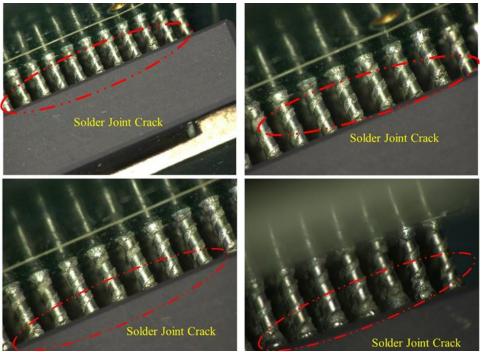

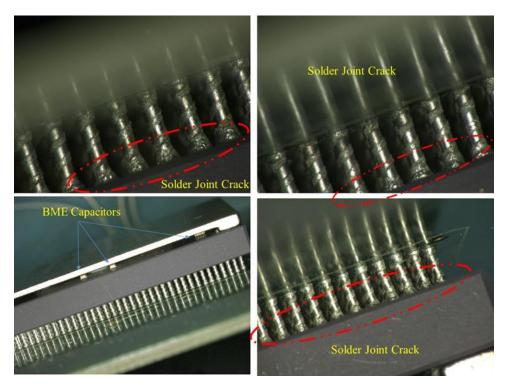

Figure 13: Optical image of the solder joints cracks after 2500 thermal cycles

Figure 14. Optical Image of the CCGA 1752 Packages after 2500 Thermal Cycles

At 2500 thermal cycles, intermittent failure of the daisy chain was further pronounced, as shown in Figure 15.

#### Time

Figure 15. Resistance vs. Time around 2500 Thermal Cycles

The CCGA test articles were inspected prior to thermal cycling and after 623, 1460 and 2500 thermal cycles. The daisy chains were monitored continuously during the thermal cycling from the beginning of the test. Failures were observed in CCGAs tested under extreme-temperature thermal cycling. The first failure was observed in the test article at the 1479th thermal cycle performed from -40°C±25 to +125°C. This failure was intermittent but reproduced in subsequent thermal cycles. There were several failures during the complete thermal cycling test for 2500 cycles. The  $\Delta T$  of this test was 165°C, which is slightly more than NASA standard thermal cycles ( $\Delta T = 155^{\circ}C$ ; temperature range = -55°C to +100°C). The CCGA solder joint showed an open circuit or high resistance when the board was at high temperature and a closed circuit when the board was at low temperature and vice versa. Figures 13 and 14 show optical photographs of the complete CCGA packages as inspected after 2500 thermal cycles. Several micrographs show significant damage to solder joints, particularly notably at the corners of the package. Some of the columns are cracked and displaced from their original solder-joint position. Several cracks in the solder joints were observed. The failures occurred at the column-and-board interface and at the column-and-ceramic interface. Figures 13 and 14 clearly show the failed solder joints, cracking of the column interconnects, and displacement of columns from their original position, especially at the corners of the package.

#### CONCLUSIONS

CCGA 1752 (CN version) packaging interconnect technology test boards were subjected to extremetemperature thermal cycles. The change in resistance of the daisy-chained CCGA interconnects was measured as a function of increasing number of thermal cycles. A catastrophic intermittent failure was observed after 1479 extreme-temperature thermal cycles based on continuous electrical-resistance measurements. The test was continued for 2500 thermal cycles so that investigators could corroborate and understand the test results. X-ray and optical inspections were done before thermal cycling. Failures were observed based on electrical-resistance measurements during extreme-temperature thermal cycling after the 1479th thermal

cycle. Daisy chains were open during the hot cycle and recovered during the cold cycle.

- CCGA packages were tested from +125°C±3 to -40°C±25 for 2500 thermal cycles.

- The first failure was observed at the 1479<sup>th</sup> thermal cycle for a  $\Delta$ T of 165°C.

- Corner columns failed first and showed cracks. One failure mechanism was realized. Failure of solder fillet was observed.

- After extensive thermal cycling, solder was cracked along the columns, as evident from optical digital photographs.

- Optical (conclusive) imaging was used to inspect the CCGA vs. thermal cycles.

## ACKNOWLEDGEMENTS

The research work described in this paper was carried out at the Jet Propulsion Laboratory, California Institute of Technology, Pasadena, CA. I would like to thank Ryan Ross, Mohammad Mojarradi, Jeremy Bonnell, Atul Mehta, Reza Ghaffarian, James S. Howard, Jong Ook Suh, Steve Tseng, Kristen Macneal, Charles J. Kaczinski, Mau Tran, Mimi Paller, Khanara Ellers, Mike Blakely, Keith Novak, Jacki Lyra, Steven Schroder, Andrew Johnson, Mark Underwood, Cate Harris, Heidi Nichols, Randy Dodge, Colin McKinney, Jeff Srinivasan, Gun-Shing Chen, and Doug Sheldon for their interest, discussions, and constant support. The Mars 2020 project is highly appreciated for encouraging me to address qualification of the CCGA (CF version) for potential use in the spacecraft's Vision Compute Element (VCE). Thanks are due to Javeck Verdugo for the some optical inspection of package. Thanks are due to Marie-Peterson, Claire for her help in editing the manuscript.

#### REFERENCES

[1] R. Ramesham, "Reliability of Ceramic Column Grid Array (CCGA717) Interconnect Packages Under Extreme Temperatures for Space Applications", <u>Journal of</u> <u>Microelectronics and Electronic Packaging</u> 7, 2010, pp. 16– 24.

[2] International Business Machines Corporation (IBM), "Ceramic Column Grid Array Assembly and Rework User's Guide", July 25, 2002.

[3] A.C. Mehta, "A Report on BGA/CGA Assembly and Rework Qualification", Personal Communication, JPL, Pasadena, CA, August 31, 2007.

[4] A.C. Mehta and C.C. Bodie, "Column Grid Array Rework for High Reliability", <u>The Annual Pan Pacific</u> <u>Microelectronics Symposium & Exhibit</u>, February 10–12, 2009, Hapuna Beach Prince Hotel, Big Island, Hawaii, pp. 331–340.

[5] R.N. Master, M.S. Cole, and G.B. Martin, "Ceramic Column Grid Array for Flip Chip Applications", <u>Proceedings</u> of 45<sup>th</sup> Electronic Components and Technology Conference, 1995, pp. 925–929.

[6] Aeroflex Colorado Springs, "Solder Column Qualification for Ceramic Column Grid Array (CCGA)", White Paper, October 2006. [7] R. Kuang, L. Zhao, Actel Corporation, CCGA Thermal Test Report (26 pp.).

[8] R. Ghaffarian, "Thermal Cycle Reliability of PBGA/CCGA 717 I/Os", Proceedings of 56<sup>th</sup> Electronic Components and Technology Conference, 2006.

[9] R. Ghaffarian, "Effect of Area Array Package Types on Assembly Reliability and Comments on IPC-9701A", NASA Electronic Parts and Packaging Program (NEPP) Guideline Document, <u>APEX</u>, 2006.

[10] R. Ghaffarian, "Thermal Cycle Reliability and Failure Mechanisms of CCGA and PBGA Assemblies with and without Corner Staking", <u>IEEE Transactions on Components</u> and Packaging Technologies, 31, June 2008, pp. 285–296.

[11] R. Ghaffarian, "CCGA Packages for Space Applications", <u>Microelectronics Reliability</u>, 46, 2006, pp. 2006–2024.

[12] A. Tasooji, R. Ghaffarian, and A. Rinaldi, "Design Parameters Influencing Reliability of CCGA Assembly: A Sensitive Analysis", <u>IEEE Intersociety Conference on</u> <u>Thermal and Thermomechanical Phenomena; 56th</u> <u>Electronic Components and Technology Conference</u>, San Diego, California, May 30 to June 2, 2006, pp. 1056–1063.

[13] Actel Space Forum, "CCGA Package Testing Data Review", <u>MRQW</u> 2005, Dec 7, 2005.

[14] Actel Corporation, "Ceramic Column Grid Array Package", Application Note, September 2003.

[15] J. Lau and W. Dauksher, "Reliability of a 1657 CCGA Package with 95.5 Sn, 3.9 Ag, and 0.6 Cu on Lead-Free Solder Paste on PCBS", <u>J. Electronic Packaging</u>, 127(2), pp. 96–105.

[16] R. Ghaffarian, "Update on CGA Packages for Space Applications", <u>Microelectronics Reliability</u>, 2016.

[17] Topline (dummy electronics packaging component vendor) CCGA Library.

[18] S. Mattsson, "Atmel CGA 625 Mounting Evaluation", <u>ESTEC</u>, May 22, 2007.

[19] R.L. Claize, H.E. White, M. Craig, E. Wynn, and W.M. Robinson, "Solidcolumns CCMD Test Report on Serial Thermal Cycles, Shock, and Vibration Tests", Raychem Corporation Test Report (TR) 1003, 3/5/1987.

[20] A. Copus, "Thermal Performance of Micro-springs in Electronic Systems", NASA USRP Internship Final Report, Marshall Space Flight Center, Reviewed by Jeff Brown, July 31, 2009.

[21] G. Alcorn, S. Scott, J. Bruner, D. Andrucyk, "Ceramic Column Grid Array Design and Manufacturing Rules for Flight Hardware", GSFC-STD-6001, February 2011.

[22] J. Fleisher and W. Willing, "Study of Column Grid Array Components for Space Systems", Northrop Grumman Corporation, 2011.

[23] S. Tripathi, H.M. Patel, S.A. Patil, D.K. Pandey, I.L. Prajapati, C.N. Joshi, R.S. Sharma, and R. Arora, "Ceramic Column Grid Array Assembly Qualification and Reliability Analysis for Space Missions", <u>IEEE Transactions on Components</u>, Packaging, and Manufacturing Technology, 5(2), February 2015, 279.

[24] J. Fabula, "A Review of the CF Package and Implications of Addendum Y", <u>MRQW</u> 2010.

[25] <u>NASA Handbook: Requirements for Soldered Electrical</u> <u>Connections</u>, NHB-5300.4 (3A-1), December 1976.

[26] <u>Reliability Hotwire</u>, 22, December 2002 and 21, November 2002.